封装行业正在努力将小芯片(chiplet)的采用范围扩大到几个芯片供应商之外,为下一代 3D 芯片设计和封装奠定基础。

新的小芯片标准和用于确定给定基于小芯片的设计可行性的成本分析工具是两个新的重要部分。与其他努力一起,他们目标是推动小芯片模型向前发展,尽管该技术仍存在挑战和差距。

使用这种方法,封装公司可以在库中拥有具有不同功能和工艺节点的模块化芯片或小芯片“菜单”。然后,芯片客户可以选择这些小芯片中的任何一个,并将它们组装在一个先进的封装中,从而产生一种新的、复杂的芯片设计,作为片上系统 (SoC) 的替代品。

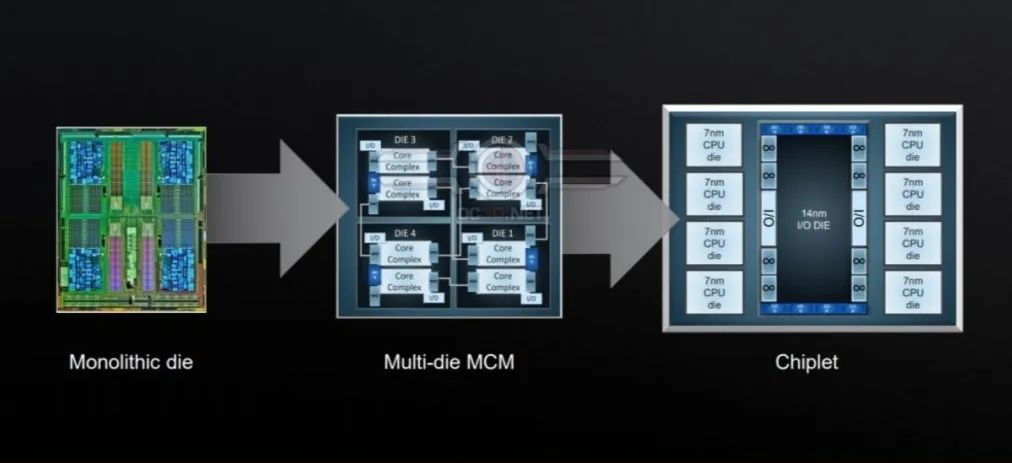

小芯片模型已被英特尔、AMD 和 Marvell 等公司证明有效,这些公司设计自己的小芯片和互连。现在,该行业的其他公司正在探索小芯片,主要是因为扩展对许多人来说变得过于困难和昂贵,而且迁移到新节点的功率和性能优势正在缩小。高级封装提供了一种在不同技术节点上组合芯片的经济高效的方式,而小芯片则提供了增加互连 RC 延迟的解决方案。它们还承诺更快地开发复杂芯片,并且可以针对特定市场和应用进行定制。

传统上,为了开发复杂的 IC 产品,供应商设计了一种将所有功能集成在同一芯片上的芯片。在随后的每一代中,每个芯片的功能数量都急剧增加。在最新的 7nm 和 5nm 节点上,成本和复杂性飙升。(节点是指特定的过程及其设计规则。)

“设计新硅节点的成本正在上升,”谷歌高级技术开发工程师 Mudasir Ahmad 在最近的一次演讲中说。“只是为了给你一个规模,现在做 5nm 芯片的成本与做 10nm 和 7nm 芯片的成本加起来差不多或差不多。它非常昂贵。”

虽然传统方法仍然是新设计的一种选择,但小芯片为客户提供了另一种解决方案。但与任何新技术一样,chiplet 集成并不简单。目前,基于小芯片的设计专门用于高端产品,而不是日常设计。即便如此,构建基于小芯片的模型也需要几个部分。只有少数大公司拥有所需的内部专业知识和能力,其中大部分是专有的。

这将基于小芯片的方法的采用限制在少数人身上。但现在,行业正在努力使基于小芯片的设计更易于访问。这些努力包括:

通常,要开发基于小芯片的设计,第一步是定义产品。然后,提出的基于小芯片的设计需要几个部分,例如产品架构、已知良好的芯片 (KGD) 和芯片到芯片的互连。它还需要完善的制造策略。

KGD 是设计中使用的裸片或小芯片。芯片到芯片互连允许小芯片在设计中相互通信。通过开发或采购这些部件,芯片客户可以开发基于小芯片的设计,至少在纸面上是这样。

但最大的问题是该设计是否可行或具有成本效益。这可能是一个主要的绊脚石,阻止了对风险不利的芯片客户考虑小芯片。

为了帮助这里的客户,ODSA 发布了一个成本分析软件工具,其中包括开发基于小芯片的设计所涉及的所有可能组件和成本的电子表格。

“没有通用规则说你应该总是做小芯片,或者你不应该做。这一切都取决于特定的应用程序,”谷歌的Mudasir Ahmad说。“我们需要一个可用于每个应用程序的模型来提供反馈。[使用电子表格,芯片客户](With the spreadsheet, chip customer)可以使用通用框架将数据输入其中。然后他们可以尝试了解为特定应用程序制作小芯片是否有意义。”

成本不是唯一的因素。工程师还必须考虑小芯片的挑战。根据Ahmad的说法,以下是其中一些挑战:

-

报废成本:如果一个小芯片在一个或多个最终设计中失败,则设备可能会报废。这增加了废品成本。

-

测试:为了最大限度地减少废品损失,设计需要更多的测试覆盖率。

-

性能:将信号从一个芯片移动到另一个芯片可能会降低产品的性能。

商业模式是另一个挑战。“如果您有不同的供应商提供不同的零件,并且您将它们全部放在一个封装中,那么谁负责什么?谁承担失败的责任?” Ahmad问道。

成本和技术挑战只是小芯片等式的一部分。客户还必须定义产品并为设计选择架构。

这里有很多选择。客户可以将芯片集成到现有的高级封装或新架构中。

扇出是一种选择。在扇出封装的一个示例中,DRAM裸片堆叠在封装中的逻辑芯片上。

在高端系统中使用,2.5D是另一种选择。在 2.5D 中,裸片堆叠在中介层上,或并排连接。中介层包含硅通孔(TSV),它提供了从die到电路板的电气连接。在一个示例中,ASIC 和高带宽存储器(HBM) 并排放置在中介层上。HBM 是 DRAM 内存堆栈。

另一种选择是将小芯片合并到新的 3D 架构中。例如,英特尔正在开发一种 GPU 架构,代号为 Ponte Vecchio。该器件在一个封装中集成了 5 个不同工艺节点的 47 个tiles或小芯片。

图 1:高性能计算封装的不同选项,基于中介层的 2.5D 与基板上扇出芯片 (FOCoS)。资料来源:ASE

图 2:2.5D 封装、高密度扇出 (HDFO)、带桥接封装和小芯片的更多示例。资料来源:安靠

任何基于小芯片的架构都需要已知良好的裸片,即满足给定规格的裸片。如果没有 KGD,封装可能会出现低良率或在现场失败。

“我们收到裸片,然后将它们放入封装中,以提供具有功能的产品,” ASE工程和技术营销总监Lihong Cao在最近的一次活动中说。“关于 KGD,我们希望通过良好的功能对其进行全面测试。我们希望它是 100%。”

这不是唯一的挑战。在一个封装中,一些die是堆叠的,而另一些则位于其他地方。因此,您需要一种使用裸片到裸片互连将一个裸片连接到另一个裸片的方法。

今天的小芯片设计使用专有互连连接芯片,这限制了该技术的采用。“小芯片成为新 IP 的最大障碍是标准化,” QP Technologies的母公司 Promex 总裁兼首席执行官 Richard Otte 说。“必须在小芯片之间建立标准/通用通信接口,才能在多个封装供应商之间实现这一点。”

好消息是,有几个组织正在为小芯片开发开放的裸片到裸片互连标准。目前有几种相互竞争的技术,尚不清楚哪种技术会胜出或如何将它们结合起来。

ODSA 正在准备一种名为 Bunch of Wires (BoW) 的芯片到芯片互连技术。其他 die-to-die 技术包括高级接口总线 (AIB)、CEI-112G-XSR 和 OpenHBI。

在最新的努力中,由英特尔、三星、台积电和其他公司支持的新小芯片联盟发布了 UCIe,这是一个涵盖芯片到芯片 I/O 物理层、芯片到芯片协议和软件堆栈的规范。

上述所有规范都定义了封装内小芯片之间的标准互连,但它们都是不同的。“UCIe 和 BoW 都是开放规范,定义了封装内小芯片之间的互连,并支持开放的小芯片生态系统。但它们与如何定义层和优化应用程序不同,”ASE 的曹说。

事实证明,没有一种互连技术可以满足所有需求。工程师将选择满足给定应用程序要求的选项。“各种标准之间存在重叠子集的区域,” JCET首席技术官 Choon Lee 说。“因此,坚持一个标准可能没有重要意义。通常,小芯片的功能块由设备制造商定义。他们知道如何优化小芯片之间的互连。”

一旦定义了chiplet 架构、KGD 和互连,下一步就是确定将产品投入生产是否有意义。

和以前一样,可以在代工厂、内存制造商或 OSAT 制造和组装封装或类似小芯片的设计。一些(但不是全部)代工厂和内存制造商拥有自己的内部封装组装业务。

每个供应商都有不同的能力。每个人都在开发一种或多种不同的方法来将不同的小芯片组装、堆叠和粘合在一起。先进的键合技术包括热压、激光辅助和铜混合键合。

热压键合 (TCB) 和激光辅助键合 (LAB) 都使用带有铜微凸块的传统倒装芯片工艺。在这个过程中,铜凸点形成在芯片上,然后使用倒装芯片键合器、LAB 或 TCB 将器件键合到另一个结构。相比之下,铜混合键合使用铜互连而不是传统的凸块来堆叠和连接die。

传统的倒装芯片工艺用于制造多种封装类型。一种称为球栅阵列 (BGA) 的类型用于多种芯片应用。

为了制造 BGA 封装,该过程首先在晶圆厂的晶圆上制造芯片。然后,在晶圆的一侧形成基于焊料材料的微小铜凸点。凸块由带有薄镍扩散屏障的铜柱和锡银焊帽组成。

铜凸块将一个die连接到另一个die或封装中的基板。这些凸块在不同结构之间提供了小而快速的电连接。制作铜凸点是众所周知的工艺。

一旦在硅片上制造了凸块,芯片就会被切割。然后,该设备经过传统的倒装芯片工艺。

首先,将裸片放置在倒装芯片键合机中。通常,倒装芯片键合机用于以 300μm 至 50μm 的凸块间距堆叠和键合裸片。今天的凸块间距延伸到 40µm 及以下。(间距是指裸片上相邻凸块之间的空间。)

“许多倒装芯片器件不需要细间距,”Kulicke & Soffa (K&S) 的首席技术官 Bob Chylak 说。“倒装芯片键合机取出芯片,将焊球浸入助焊剂中,然后将它们放置在 PCB 上。”

这个过程重复几次。最终,几个裸片被放置在 PCB 上,有时称为裸片基板。然后,它经历一个大规模回流过程。“PCB 通过回流炉,回流炉熔化焊料,然后将其固化,”Chylak 说。

在回流工艺之后,PCB 上的die会进行清洁步骤。然后,系统会在 PCB 上的每个凸块die上注入模塑料。国立中山大学研究员 Wan-Chun Chuang 在一篇论文中说:“[这密封]了所有组件,保护了设备内部的芯片和凸块。”

然后,将较大的 C4 焊球植入基础 PCB 基板下方。最后,将 PCB 上的管芯切块,创建单独的 BGA 封装,每个单元内部都有管芯。

该行业需要一种不同的解决方案来使用最先进的铜微凸块,包括 40μm 或更紧密的间距。但在这些间距上使用传统的倒装芯片键合机具有挑战性。对于更细的间距,一些封装公司将 TCB 用于 40μm 至 10μm 凸块间距的芯片堆叠和键合应用。

通常,TCB 用于 2.5D/3D 封装的芯片堆叠和键合。

图 4:2.5D/3D 系统架构。铜微凸块连接中介层和基础管芯。资料来源:拉姆布斯

在 TCB 工艺中,使用传统的凸块工艺在die上形成微小的铜凸块。但是,在这种情况下,凸点更小,间距更小。然后,封装公司不再使用传统的倒装芯片键合机,而是使用 TCB 工具。

“不是加热整个电路板和上面的所有芯片,而是热压键合机抓住芯片,像普通倒装芯片一样将其浸入助焊剂中,然后将其放置在 PCB 上,”K&S 的 Chylak 说。“键合头中有一个加热器。这加热到超过将芯片固定到位的焊料的熔点。然后它冷却下来,使焊料凝固。”

同时,鲜为人知的选项 LAB 也是可行的。在 LAB 工艺中,使用传统的凸块工艺在管芯上形成微小的铜凸块。

然后,将凸块裸片和基板放置在 LAB 工具中。该系统使用激光产生的热量将管芯对齐并粘合到基板上。

“(实验室设备)具有红外激光源(980nm 波长)和光学系统(均质器),可产生尖锐且均匀的激光束,能够以极高的升温速度选择性地加热目标区域。JCET 高级研发工程师 Wagno Alves Braganca 在一篇论文中表示:. 其他人也为这项工作做出了贡献。

在 LAB 系统中,键合过程在不到一秒的时间内发生,热应力低。LAB 比 TCB 快,但它需要来自特定供应商的专用设备。

Amkor 和 JCET 正在开发 LAB。该技术自 2019 年左右开始投入生产。“LAB 一直在生产高性能计算应用,在这些应用中,由于翘曲或残余应力导致的非湿凸块或开裂可能至关重要,” JCET的 Lee 说。

OSAT 希望将 LAB 推至 10μm 间距左右。“我们已经使用铜无铅凸块和我们的激光辅助键合方法演示了低至 10μm 的间距。我们的产品符合 20μm 间距领域的要求。这些都是晶圆上芯片,而且大多是特种传感器,” Amkor高级封装开发和集成副总裁 Michael Kelly 说。

TCB 和 LAB 都延伸到 10μm 凸点间距。除此之外,该行业还需要一种新的解决方案,即铜混合键合。在这里,想法是使用细间距铜连接直接堆叠和连接die,而不是传统的微凸块。

铜混合键合并不新鲜。2005 年,Ziptronix 推出了一种称为低温直接键合互连 (DBI) 的技术,被认为是铜混合键合的第一个版本。(2015年,Tessera收购了Ziptronix。2017年,Tessera更名为Xperi。)

2015 年,索尼获得了 DBI 许可,并在其 CMOS 图像传感器生产线上实施了该技术。其他图像传感器供应商也获得了 DBI 许可。

对于 CMOS 图像传感器,供应商遵循晶圆间混合键合工艺流程。首先,在一个晶圆厂中处理两个不同的晶圆。第一个晶圆由大量处理器裸片组成。第二个晶圆由大量像素阵列管芯组成。

目标是将每个像素阵列die堆叠在每个处理器管芯之上。为此,将两个硅片插入硅片键合机中。键合机对齐每个芯片并使用两步键合工艺将它们连接起来。首先它形成电介质-电介质键,然后是金属-金属连接。最后,晶圆上的die被切割和封装,形成图像传感器。

使用 Xperi 的 DBI 工艺,索尼和 OmniVision 正在生产分别采用 3.1μm 和 3.9μm 间距的 CMOS 图像传感器。

现在,业界正在开发用于 3D 芯片和封装应用的铜混合键合。AMD、Graphcore 和 YMTC 已经发布了来自不同供应商的使用混合键合的产品。其他人在研发。

在封装中,混合键合用于晶圆到晶圆和芯片到晶圆的键合。在die-to-wafer中,两个带有芯片的晶圆在晶圆厂中进行加工。然后,第一晶片上的芯片被切割并使用混合键合键合到第二晶片。

图 5:Xperi 的芯片到晶圆混合键合流程。资料来源:Xperi

芯片到晶圆为封装客户提供了更多选择,但这是一个具有挑战性的过程。“CMOS 图像传感器是通过晶圆对晶圆混合键合形成的,其中键合芯片的占位面积相似,并且两个晶圆都具有足够高的良率以及成熟的硅供应链和工艺,”Xperi产品营销副总裁Abul Nuruzzaman 说,。“在 2.5D 或 3D 高级封装中,有时需要芯片到晶圆的键合技术。它还需要 KGD、不同的裸片尺寸以及来自不同技术节点或晶圆尺寸的裸片。切割、芯片处理和组装必须与混合键合工艺兼容,这对行业来说相对较新。”

除了 Xperi,Imec、英特尔、Leti、美光、三星和台积电也在开发铜混合键合工艺。

所有铜混合键合工艺都是相似的。首先,所需的芯片设计在晶圆厂的两个晶圆上进行处理。然后,每个晶圆在晶圆厂中都经过一次大马士革工艺。为此,将介电材料沉积在晶片的一侧。在材料上,为晶圆上的每个裸片图案化和蚀刻微小的通孔。

然后将铜材料沉积在硅片上。然后,化学机械抛光 (CMP) 工具抛光表面。剩下的是每个芯片的微小通孔中的铜金属化材料。暴露的铜通孔代表焊盘。

硅片的表面必须是原始的,没有缺陷。因此,在 CMP 之后,使用计量工具检查表面拓扑结构是否存在缺陷。然后,将芯片切割在一个硅片上。使用晶圆键合机,将die堆叠并键合到第二个晶圆上。然后切割最终的键合芯片。

这是一个具有挑战性的过程。在流动过程中,不需要的颗粒和缺陷可能会出现在模具上。颗粒会导致焊盘出现空洞。即使一个 100nm 的粒子落在焊盘上,也可能导致数百个连接失败。

迄今为止,只有少数供应商开发和制造了基于小芯片的设计。为了更广泛地采用该技术,几个关键部分正在到位。

鉴于在先进节点开发芯片的成本不断上升,业界比以往任何时候都更需要小芯片模型。

微信

微信 QQ

QQ 微博

微博