Lumerical案例 | 基于热感知的WDM收发器光子电路仿真——Icepak集成

2026年2月2日 15:07

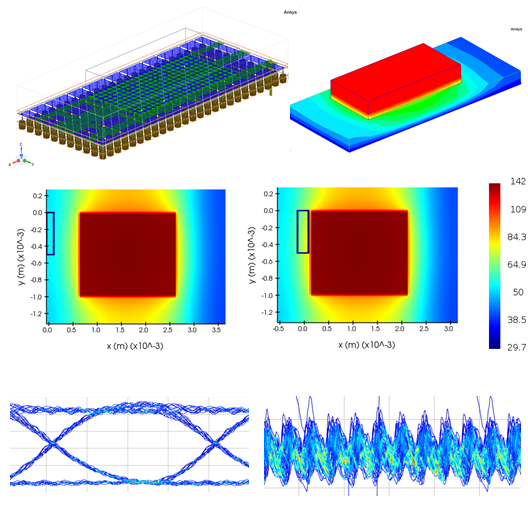

2026年2月2日 15:07在这个例子中,Ansys Lumerical INTERCONNECT的光子集成电路(PIC)建模能力与Icepak强大的热仿真能力相结合,用于仿真和设计波分复用(WDM)收发器,同时考虑封装中其他区域(例如电子集成电路(EIC)、印刷电路板(PCB) 等)的发热。

一、概述

本文以一个六通道WDM系统为例进行研究。该系统采用共封装光学器件(CPO)设计,包含光电器件。由于电子集成电路(EIC)和印刷电路板(PCB)产生的热量,紧凑型CPO内部的温度变化会影响硅光子元件的性能。本文旨在:1)通过热仿真了解CPO内部的温度分布;2)找到电路板上WDM元件的理想位置,以减轻电子元件发热带来的不利影响。

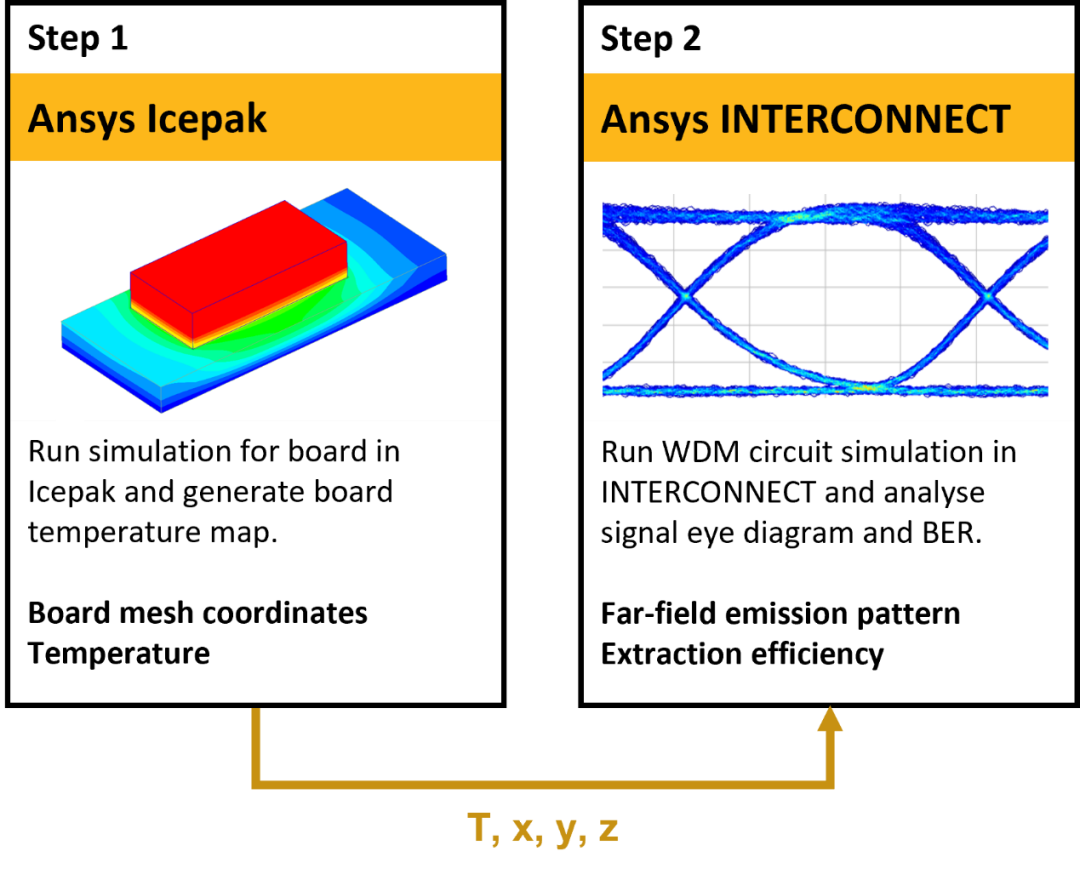

首先,使用Icepak对整个封装进行热仿真。然后可以生成光子(硅)层的温度分布图,并将其导出以用于光子电路仿真。

接下来,将温度分布图导入INTERCONNECT软件。INTERCONNECT软件针对晶圆上不同的光学元件位置运行多次仿真。基于扫描结果,分析眼图和误码率(BER)等性能指标,以确定晶圆上光学元件的理想布局。

步骤 1:Icepak中进行热仿真

Icepak在运行时计算封装温度,并导出硅晶片网格坐标和相应的温度。

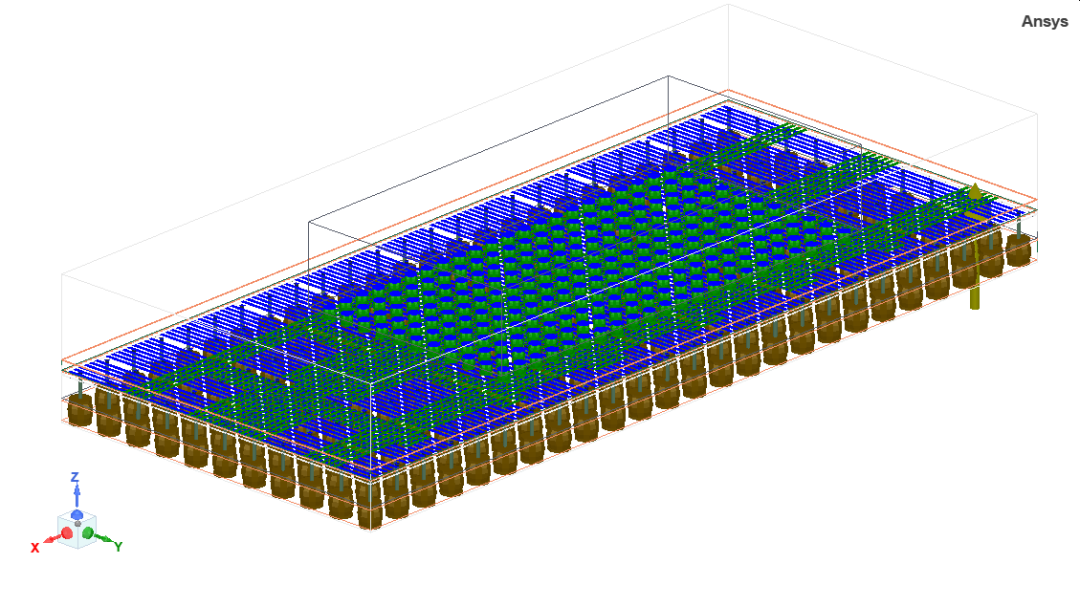

上图展示了用于热分析的PCB板设计示例。绿色层为硅片,棕色层为PCB板。PCB板与硅片之间采用球栅阵列(BGA)连接。透明框内为位于PCB板顶部的集成电路(EIC),EIC用作热源以启动PCB板的热分析。在本例中,我们将EIC视为均匀热源,用户也可以加载EIC的功率分布图以进行更复杂的热分析。

本次热仿真中,EIC加热数据来自芯片热模型(CTM),焦耳加热数据则来自SIwave。晶圆底部温度设定为50℃,顶部采用自然对流换热系数(HTC)。

注意:要导出温度图,用户需要使用Icepak的“Write Thermal Loads”ACT扩展。

步骤 2:在INTERCONNECT中进行Circuit仿真

在INTERCONNECT中,WDM传输链路被用作测试平台。INTERCONNECT导入上一步生成的温度分布图,并使用脚本在晶圆上分配WDM系统。WDM电路中光器件的温度根据晶圆的温度分布图进行设置。仿真中使用的紧凑模型(由CML Compiler生成)对温度敏感,并会根据更新后的温度调整模型的性能。然后,INTERCONNECT运行电路仿真并获得性能指标结果(误码率和眼图)。通过比较不同位置(以及相应的不同温度)的结果,我们可以确定PIC元件的理想位置。

二、运行和结果

步骤 1:Icepak中进行热仿真

- 在Icepak中打开并运行文件Thermal_simulation.aedtz。如果ACT扩展被隐藏,请使用“Show/Hide ACT Extension”按钮显示它们。导航至“Write Thermal Loads”扩展程序,并设置“Destination Folder”以保存温度图文件。点击扩展程序中的“Finish”,.txt格式的温度图将保存到指定的目标文件夹。

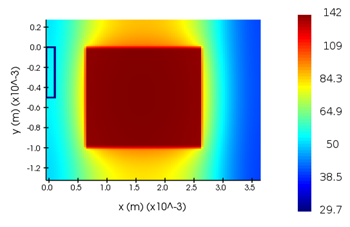

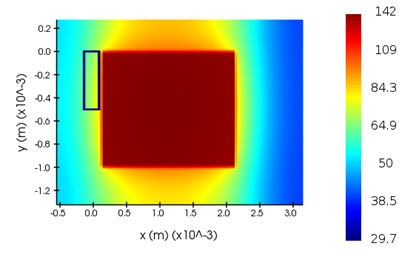

下图显示了整个电路板的温度。温度分布图文件保存了电路板的网格(x、y和z坐标)及其对应的温度。

步骤 2:在INTERCONNECT中进行Circuit仿真

Wafer上optical board默认分配情况下的电路性能:

- 打开文件WDM_6_channel.icp。这是一个包含六通道WDM电路的测试平台。其构建组件来自Demo_CML紧凑模型库(CML)。将Demo_CML.cml安装到元素库中的Design Kits文件夹,然后刷新(File/Refresh)该文件。在脚本编辑器中打开并运行temp_set_up.lsf脚本。该脚本将调用load_temp_map.lsf脚本,并根据整个晶圆上optical board x轴和y轴偏移量,设置电路中各元件的温度。运行INTERCONNECT仿真,绘制6个通道的眼图,并在眼图分析仪中记录BER值。

temp_set_up.lsf脚本会生成指定z轴位置的晶圆温度图。由于光学元件的高度相对于整个电路板而言较矮,我们假设光学元件在z轴方向上的温度分布均匀,并脚本中固定一个z值来生成温度图。图中深蓝色方框表示光学电路板,以便我们了解光学电路板在晶圆上的位置以及其在该位置的工作温度。

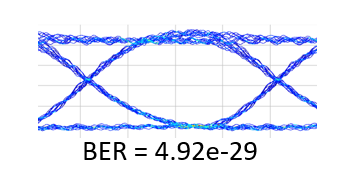

默认设置下,optical board位于晶圆上0mm处,该位置的工作温度约为60摄氏度。考虑到其他布线限制和温度因素(ring models的调谐功耗极小),这是optical board的理想放置位置之一。以下是通道1的眼图和误码率(BER):

改变optical board在wafer上的位置后Circuit性能的变化(对比结果):

- 打开文件WDM_6_channel.icp。返回设计模式,在temp_set_up.lsf中,更新为-0.5mm(-0.5e-3m)。运行INTERCONNECT仿真,绘制6个通道的眼图,并在眼图分析仪中记录BER值。回到设计模式,打开并运行set_tunning_voltages.lsf脚本,为当前温度下的环形调制器和谐振器设置理想调谐电压。重复步骤2并记录结果。

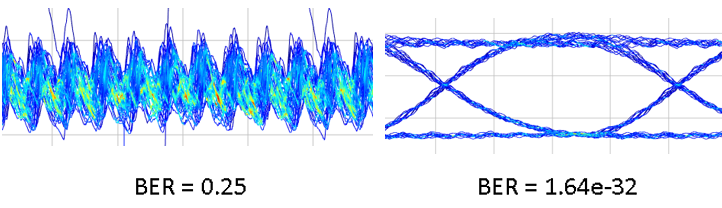

Circuit中的环形调制器和谐振器均设计有热调谐功能。set_tuning_voltages.lsf脚本会根据环形调制器和谐振器的工作温度设置其调谐电压。通过这种热调谐功能,环形调制器和谐振器的性能能够稳定地适应温度变化。

将optical board放置在晶圆原点,工作温度约为70摄氏度。以下是通道1在未进行和进行ring models热调谐后的眼图和误码率(BER):

环形调制器和谐振器模型显示了环的调谐电压和功率。重新校准环形调制器和谐振器分别需要约0.022W和0.015W的功率。

三、使用您的参数更新模型

使用新的CML:该电路的基本构建模块来自Demo_CML,而Demo_CML又基于lumfoundry_template CML。用户可以将这些构建模块替换为其他CML中的模型,从而生成WDM电路。

自定义评价指标:在本例中,我们使用误码率(BER)和信道眼图作为评价指标来判断电路性能。我们注意到,通过对环形调制器和谐振器进行热调谐,可以使电路在温度范围内保持相对稳定的工作状态。如果眼图干净且误码率接近于0,我们可以选择其他评价指标,例如误差矢量幅度(EVM),作为判断电路性能的标准。

四、进一步拓展模型

集成多种工具进行全电路优化

在另一个例子中,我们演示了如何利用optiSlang互操作性对不同的Lumerical求解器进行协同优化:Optimizing Traveling Wave MZM-optiSLang Interoperability。本示例中所示的工作流程可以进行调整,以进行基于optiSlang的全电路优化,并考虑热效应。

Optimizing Traveling Wave MZM-optiSLang Interoperability

相关链接:https://support.lumerical.com/hc/en-us/articles/4403299362195

使用其他test-bench线路

本示例使用六通道WDM收发器作为温度效应的性能测试平台。但它也可以适用于其他电路。您可以创建不同的测试平台仿真文件,以便根据需要提取结果。

Ansys软件试用,培训,欢迎联系摩尔芯创。

五、其他资源

- Wavelength division multiplexing

相关链接:https://support.lumerical.com/hc/en-us/articles/360042322774

- Optimizing Traveling Wave MZM - optiSLang Interoperability

工程师必备

- 项目客服

- 培训客服

- 平台客服

TOP