五分钟看完SiP设计EDA流程

2022年9月8日 10:45

2022年9月8日 10:45EDA设计工具在SiP实现流程中占有举足轻重的地位。文章在介绍Cadence 产品的基础上,同时梳理和补全了业界常用的其他几大EDA公司的主流SiP设计与仿真工具。供大家参考和学习。

--------设计工具--------

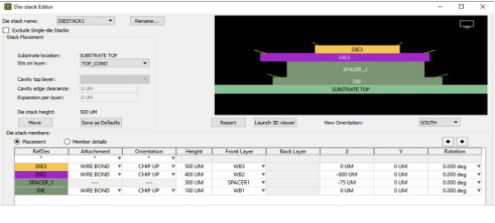

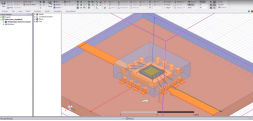

Cadence的Allegro Package Designer Plus,是封装设计业内的准行业标准工具,可实现WireBond、FlipChip、SiP、Chiplet异构集成,2.5D/3D硅基封装的设计与验证。对于SiP系统级封装产品来说:

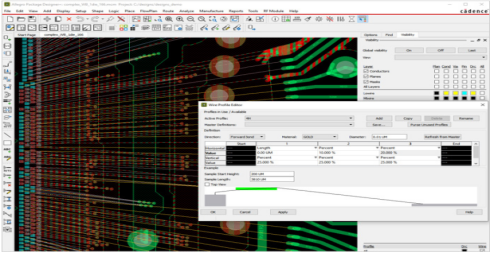

01、可实现裸芯,无源器件在基板上的构建,封装基板的叠构,支持Wirebond金(铜)线设计,HDI微孔结构设计,基板布线设计,及多种类后处理。

02、其基于Constraint Manager的规则设计,提供了一个高可靠性的设计/可制造性/信号完整性一体化平台。

03、制造方面,提供几乎所有种类的生产文件如ODB++,Gerber274X等等。

04、与Cadence 自身的Sigrity系列,Celcius系列,Clarity系列仿真软件无缝集成,软件内部的模型参数导出工具可将基板参数直接在仿真工具中进行编辑,缩短了仿真验证前期准备的耗时。

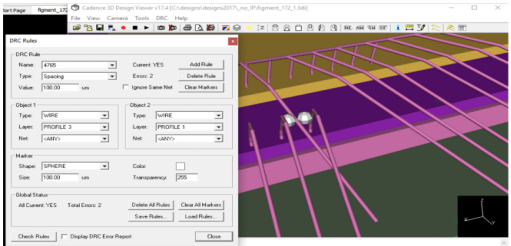

05、其具有的3D编辑器与主流仿真软件的仿真模型一体化关联,保证了SiP封装在2.5D/3D热仿真,3D力学仿真验证领域数据的一致性与准确性。

06、支持多用户在同一界面下完成设计及检查。

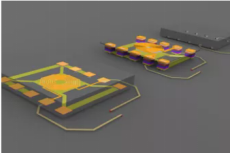

(裸芯叠构示意)

(Wire Bond 设置)

(3D检查)

在SiP设计完成后,我们通常需要对SiP封装的电性能及热性能进行电热协同仿真,以保证封装产品的可靠性。针对封装SIP的仿真分析工具主要分为四大类:一是封装模型的提取、建模工具,二是电源完整性及信号完整性分析工具,第三类为电热协同仿真工具,最后则为热力结合仿真工具。

--------模型提取工具--------

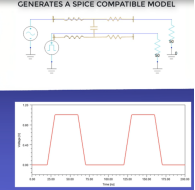

◆ XtractIM 是一款专门针对IC封装的宽带模型提取及封装性能评估工具。XtractIM能够生成标准的IBIS格式和SPICE子电路格式的封装模型。提取出的模型可以是各引脚或各网络的RLC网表,可以是带耦合参数的矩阵,也可以是Pi/T型SPICE子电路。XtractIM生成的模型可以用来评估封装模型电性能的好坏,也可用于系统级的SI和PI的仿真。

◆ XcitePI 是以芯片为中心的仿真和模型提取工具,可以用来设计和验证电源分配网络(PDN)和高速I/O。XcitePI可以提取芯片PDN模型和I/O互连模型。用户可以选择对部分结构或者整个芯片提取模型。模型提取考虑到整个芯片电源网格所有导体的寄生电阻,电容和电感的耦合。XcitePI提取的模型可以进一步用在系统级分析或者芯片-封装-PCB的协同设计。XcitePI还支持时域和频域的芯片PDN仿真,评估I/O电源地和信号的性能。

◆ PowerSI可以为PCB和IC封装提供快速准确的通用频域电磁场分析,如S参数、Z参数的模型提取,空间模式下的噪声耦合分析,EMC/EMI分析,谐振模式分析,走线阻抗和耦合检查等。从而有助于解决高速电路设计中日益突出的各种PI和SI问题:如信号和电源网络布线质量的定量分析和耦合分析,电源平面的噪声分布和去耦电容的放置,封装的电磁辐射,封装结构中可能存在的谐振模式,以及走线的整体阻抗检查和耦合分析等。PowerSI可以在布局布线前用于创建PI和SI的布线规范,也可以在布局布线后用于发现或改善潜在的设计风险。

◆ Clarity 3D求解器是一款针对互联PCB,IC封装和系统集成封装设计的3D电磁(EM)仿真工具。Clarity 3D Solver可在设计5G,汽车,高性能计算(HPC)系统和具有高标准精度的机器学习应用程序时解决最复杂的电磁(EM)挑战。业界领先的Cadence分布式多处理技术使Clarity 3D解算器能够提供几乎无限的容量和10倍的速度,从而有效地解决更大、更复杂的结构问题。它创建了高度精确的S参数模型,用于信号完整性(SI),电源完整性(PI)和电磁兼容性(EMC)分析,使仿真结果与实验室测量相匹配。Clarity 3D Solver可以通过有效地将可用计算资源与设计大小相匹配来解决真正的3D结构。

◆ Ansys Q3D Extractor是现代电子设计中的寄生提取工具。Q3D Extractor用于计算电子产品频率相关电阻、电感、电容和电导(RLCG)的寄生参数。它适用于高速电子设备中设计先进的电子封装和连接器。也可用于电力配电、电力电子和电力驱动系统中使用的大功率母线和功率变换器部件。提取出的寄生参可用于后续的SI/PI完整性分析,是使用广泛的参数提取工具之一。

(图片来源Mentor网站)

◆ Ansys HFSS 与Cadence Clarity为同类型3D全波电磁场仿真工具,HFSS可分析整个电磁场问题,包括反射损耗,衰减,辐射和耦合等。HFSS的强大功能基于有限元算法与积分方程理论,以及稳定的自适应网格剖分技术。该网格剖分技术可保证其网格能与3D物体共形并适合任意电磁场问题分析。HFSS可自动根据用户指定的几何模型,材料属性以及求解频段来生成最适合,最有效和最准确的网格进行求解,以保证求解的精度。求解较为苛刻的高频仿真问题时,所有的HFSS求解器可配置高性能计算(HPC)技术,如区域分解法和分布式求解,高性能计算可减少计算时间,有效利用计算机资源来加速求解电大尺寸问题。

(图片来源Ansys网站)

--------电源完整性及信号完整性分析工具--------

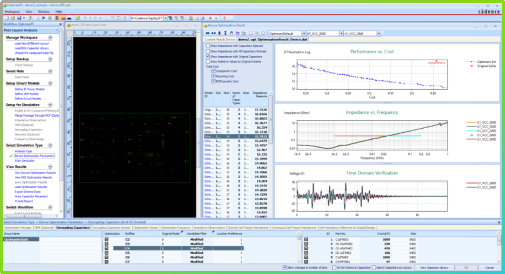

◆ OptimizePI 应用Sigrity的电磁分析和优化算法可以使IC封装PDS网络的性能或成本达到最优。OptimizePI可以帮助设计人员自动地在合适的位置放置合适容值的去耦电容,来确保产品设计以最低的成本或最小的面积满足电源分配系统(PDS)的性能目标,优化电源平面谐振,或者在不增加电容种类的情况下实现最佳的PI、EMI性能。

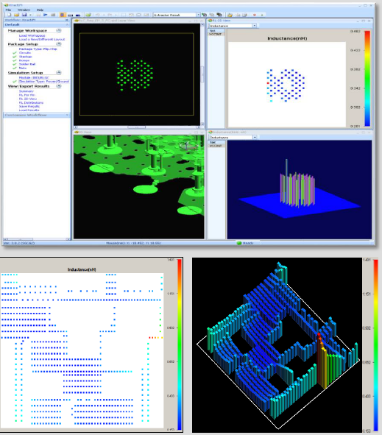

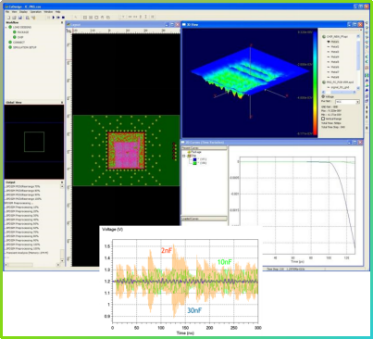

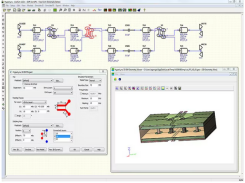

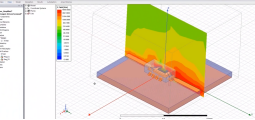

◆ PowerDC 能对IC封装提供快速准确的直流分析和电热协同分析,是一款能对基板和IC封装设计进行电热协同仿真分析的工具,其提供了一个详细的工作流程帮助仿真工程师发现设计中隐含的直流压降问题、电流密度问题和热可靠性问题。PowerDC能支持多Die堆叠的封装设计,能进行复杂设计的DRC检查,可以得到Die、过孔和封装等各组件的温度,还可以得到JEDEC定义的各种封装热参数模型。

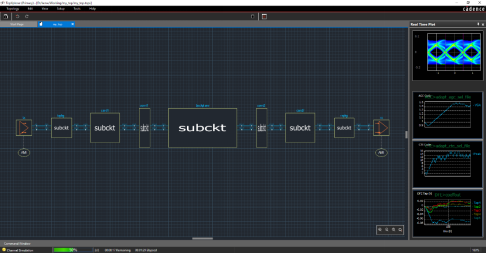

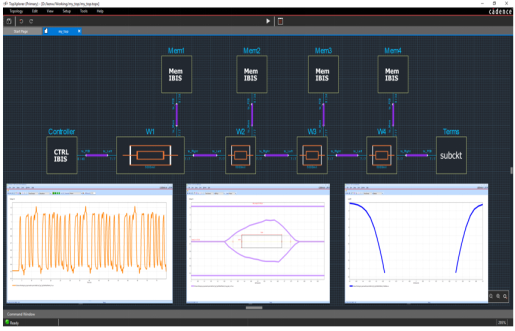

◆ SystemSI Serial Link Analysis是专用于高速SerDes接口(如PCI-e, HDMI, SFP+, XAUI, Infiniband, SAS, SATA, USB等)进行系统级芯片到芯片验证的仿真工具。SystemSI-SLA时域、频域和统计分析相结合的技术确保高速串行互连分析的效率和仿真精度, SystemSI-SLA采用易用的模块化拓扑编辑系统网表,支持多种SPICE子电路模型(如IBIS, Device, Touchstone, BNP等),采用时域、频域和统计相结合的分析技术,通过进行无源通道频域响应分析、通道特性时域冲激分析、大容量数据码型的统计分析、误码率分析等,提取系统链路的统计眼图、浴盆曲线等特征参数,为串行链路系统性能评估提供依据。SystemSI-SLA支持各种领先的AMI/VMI模型,通过先进的串扰、抖动、噪声分析和灵活的参数扫描分析,并充分考虑信号反射、串扰、码间干扰、SSN等对信号质量的影响。

◆ SystemSI Parallel Bus Analysis 是专门针对源同步高速并行总线接口(如DDRx)而开发的系统级芯片到芯片验证工具。SystemSI-PBA的前仿真能力(包括3D全波Via-wizard建模能力)确保精确的宽带模型能够快速产生并与其他系统模块连接。而后仿真能力允许用户加入优化的、包含更多细节信息的实际版图模型并进行最终的验证分析。所有的SI效应如导体/介质损耗、反射、ISI码间干扰、串扰以及同步翻转噪声(SSN)等都能在一个仿真引擎中同步考虑。其非理想电源仿真能力能精确模拟真实PDN噪声对信号的干扰。

◆ Ansys Slwave是验证板级及封装级的信号完整性,电源完整性及EMI分析为一体的工具。帮助设计师进行建模、模拟和验证高速信号传输的完整性及高性能电子产品中电源完整性。它可以准确地提取了千兆SERDES和内存总线的IBIS 及IBIS-AMI模型进行分析,保证各种产品在进入制造前设计的准确性。Slwave可实现对整个配电网络(PDN)进行全波提取,使您能够通过低压设计中的自动解耦分析来验证噪声裕度,并确保阻抗分布符合要求等。

(图片来源Ansys网站)

◆ Mentor HyperLynx SI基于IBIS或是SPICE模型评估并行(如DDR)及高速串行总线的信号完整性,包括过冲,下冲, 振铃,非单调性, 符号间干扰等等。优化信号的拓扑结构并分析信号间的串扰,结合仿真结果对设计提供最优的改善措施。通过时域或频域的方式评估互连状态以确保信号低误码率的有效传输。HyperLynx SI同时也支持基于IBIS-AMI模型,集成全波三位电磁场求解器针对高速SerDes链路进行快速且精准的分析。

(图片来源Mentor网站)

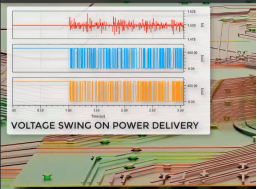

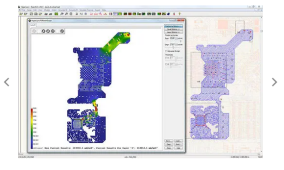

◆ Mentor HyperLynx PI 支持 AC, DC 多种类电源分析功能,分析直流压降,保证电源的载流能力。同时支持PDN分析找到最优的去耦电容策略和电容的数量和摆放位置,从而使芯片管脚处的电源波动稳定在噪声容限之内。

(图片来源Mentor网站)

--------电热协同仿真工具--------

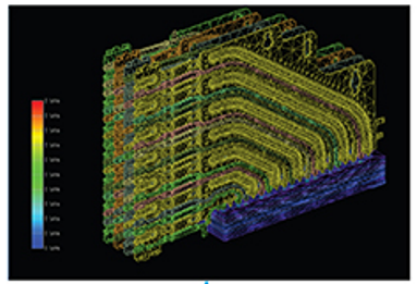

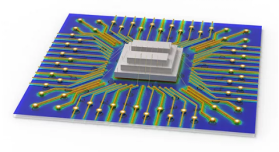

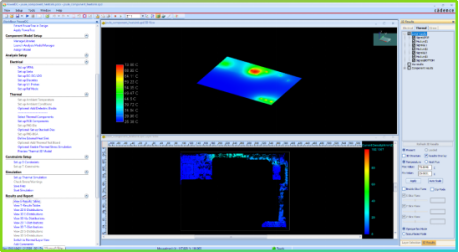

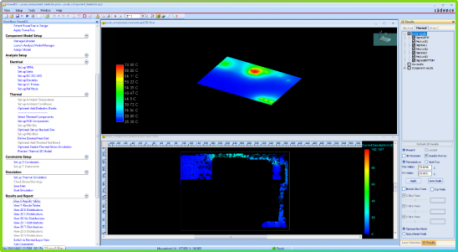

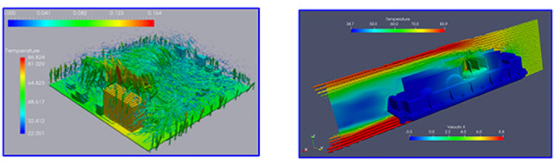

◆ Celsius Thermal Solver 是业内针对从集成电路到物理部件全电子系统所设计的一款完整电热协同仿真解决方案。Celsius Thermal Solver能够与Cadence IC、封装和基板设计平台实现无缝集成。利用创新的多物理场技术应对这些挑战。将实体结构有限元分析(FEA)与计算流体动力学(CFD)相结合,Celsius Thermal Solver可以在同一工具内完成系统分析。Celsius Thermal Solver帮助工程团队结合电气和热力分析,进行电力和热力流动仿真,从而获得比传统工具更精确的系统级热力仿真结果。此外,Celsius Thermal Solver基于先进3D 结构中电力的实际流动,执行静态(稳态)和动态(瞬态)电热协同仿真,提供了对真实世界系统行为的预见性。

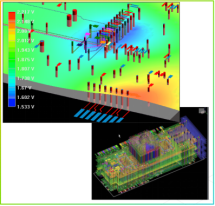

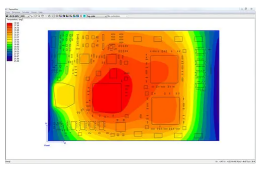

◆ Ansys最新的SIwave版本中,集成了SIwave-Icepak电热协同仿真功能,设计者在单独的SIwave软件环境中,就可以同时调用SIwave 直流求解器和Icepak 三维散热(CFD)求解器,进行电热耦合分析,得到封装或板级工作时的电流密度分布以及温度分布结果,帮助设计者提前评估温度变化对封装及PCB性能的影响,预判温度分布热点,以便进行散热设计。

(图片来源Ansys网站)

--------热力结合仿真工具--------

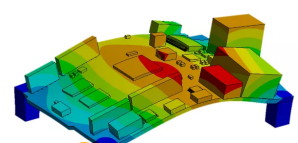

◆ 作为Ansys的核心产品之一,Ansys Mechanical是使用最广泛的的通用结构力学仿真分析系统。以结构力学分析为主,涵盖线性、非线性、静力、动力、疲劳、断裂、复合材料、优化设计、概率设计、热及热结构耦合、压电等分析中几乎所有的功能,全面集成于ANSYS新一代协同仿真环境ANSYS Workbench中。对于SiP封装来说,其功能可覆盖各类封装产品,热应力,热循环,振动,Underfill流体分析等绝大多数热力结合仿真项目。

以上就是常见的EDA设计及仿真工具,下期分享封装的质量管理,内容会持续更新,更多内容请关注图元TOPBRAIN官网(点击打开图元网站),或者图元EDA、封装与高速技术前沿公众号。

工程师必备

- 项目客服

- 培训客服

- 平台客服

TOP