半导体企业EDA仿真平台组成&计算分析及配置推荐

更新于2025年5月30日 08:43

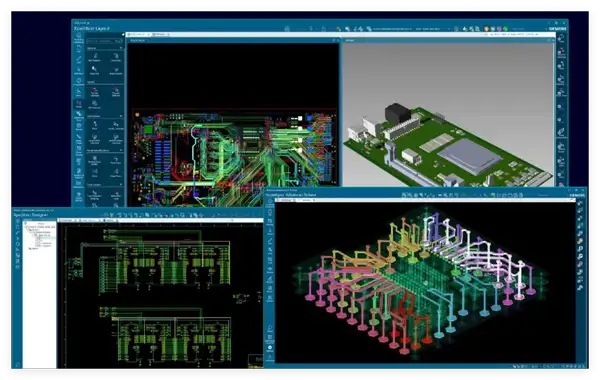

更新于2025年5月30日 08:43半导体企业的EDA(Electronic Design Automation)仿真平台,是集成电路(IC)设计和芯片设计流程的核心组成部分。它涵盖从设计前期的架构建模、功能验证,到后期的物理实现、时序/功耗仿真和制造准备等各阶段。

一、EDA仿真平台主要组成模块

No |

模块 |

主要任务 |

典型软件 |

使用阶段 |

1 |

架构与系统建模 |

高层次抽象、算法验证 |

Synopsys Platform Architect, MATLAB/Simulink, SystemC |

早期系统级设计 |

2 |

功能仿真(RTL模拟) |

验证功能正确性 |

Synopsys VCS, Cadence Xcelium, Mentor Questa |

RTL设计阶段 |

3 |

形式验证 |

无需激励验证,检查设计等价性/属性 |

JasperGold (Cadence), VC Formal (Synopsys) |

RTL阶段 |

4 |

逻辑综合 |

RTL → 门级电路 |

Synopsys Design Compiler, Cadence Genus |

综合阶段 |

5 |

时序仿真(STA) |

静态时序验证 |

Synopsys PrimeTime, Cadence Tempus |

综合后/布局后 |

6 |

功耗仿真 |

动态/静态功耗分析 |

PrimePower, PowerArtist, Voltus |

综合后、布局后 |

7 |

仿真驱动的布局布线(Place&Route) |

实现后端物理结构 |

Synopsys IC Compiler II, Innovus |

后端实现 |

8 |

电磁/信号完整性仿真 |

IR drop, Crosstalk, EMI/EMC分析 |

RedHawk (Ansys), Voltus, Totem |

后端验证 |

9 |

可靠性仿真(DFM) |

工艺可制造性、电迁移、热分析 |

Calibre (Mentor), Pegasus |

签核前 |

10 |

功能/时序仿真(门级) |

Gate-level仿真验证功能/时序 |

VCS、Xcelium、Questa(支持GLS) |

Tape-out 前 |

二、各模块的计算特点与核心算法

模块 |

核心算法 |

计算特点 |

架构建模 |

SystemC仿真、行为建模 |

单线程为主、轻计算 |

功能仿真 |

事件驱动仿真、编译仿真(编译+模拟) |

大规模波形数据、需要高IO带宽、高频编译+仿真轮转 |

形式验证 |

SAT/SMT求解、符号执行 |

内存密集、对多核支持有限(部分并行) |

逻辑综合 |

栅级映射、优化、逻辑等价 |

多核并行性一般,主要依赖单核性能 |

STA |

时序传播、路径分析、主路径查找 |

多线程支持中等,内存占用高 |

功耗分析 |

动态切换率计算、功耗建模、矢量传播 |

大量VCD/FSDB文件处理、高IO、高内存 |

布局布线 |

遍历+启发式+SAT约束优化 |

并行支持好(尤其是IC Compiler II) |

电磁/热仿真 |

FDTD/FEM/矩量法、电流网络求解 |

可GPU加速(Redhawk SC)、内存消耗大 |

版图DRC/LVS |

几何布尔操作、图匹配 |

Calibre/PEGASUS支持并行/分布式计算 |

门级仿真 |

时序精确仿真、事件驱动调度 |

IO压力高、大波形文件、高并发仿真 |

三、硬件配置推荐(按仿真任务类型)

1. 功能仿真 & 逻辑综合

CPU:Intel Xeon Gold/Platinum or AMD EPYC(频率高优先)

核心数:8~32核(RTL仿真多次并行运行)

内存:64~256 GB(视模块复杂度)

存储:高IOPS NVMe SSD(VCS/Xcelium生成大量中间文件)

网络:10GbE 或 Infiniband(用于远程License和文件访问)

2. 时序/功耗/门级仿真(GLS)

CPU:高主频多核(如Xeon Gold 6444Y,4.1 GHz+)

内存:128GB 以上(PrimeTime 或 PowerArtist)

存储:NVMe + RAID(频繁访问FSDB/VCD波形)

建议:使用局部高速缓存磁盘(如RAM Disk临时波形)

3. 后端布局布线 & EM仿真

CPU:多核心大缓存(IC Compiler II 支持 64 核+)

内存:256GB ~ 512GB(版图大时要大内存)

GPU(可选):Redhawk SC 可选 NVIDIA A100/RTX 6000 加速

4. DRC/LVS(Calibre / Pegasus)

- 分布式集群推荐:

每节点:16核、256GB 内存

分布式文件系统:NFS/Lustre/GPFS

并行调度:LSF、SLURM 或专有EDA调度器

· 存储:高速并发存储(企业级NVMe RAID、Lustre/NFS共享盘)

- Calibre DRC 强烈依赖多核心与高并发IO性能

整体EDA仿真服务器/集群建议

类型 |

推荐配置 |

单机开发工作站 |

16~32核CPU、128GB RAM、2TB NVMe SSD、RTX A6000(支持GUI仿真可视化) |

仿真专用服务器节点 |

32核、512GB RAM、4TB+ SSD + 高速网络 |

并行仿真集群 |

4~32节点、共用NFS/Lustre分布式存储、集群调度器LSF或SLURM |

EDA平台支持的并行方式总结

软件 |

并行方式 |

加速支持 |

Synopsys VCS |

多波形并行、VCS-MX分布式仿真 |

CPU集群并行 |

Cadence Xcelium |

多线程仿真、多DUT并行仿真 |

多核CPU |

PrimeTime |

多路径并行时序分析 |

支持多核但效率有限 |

Calibre |

分布式规则分区 |

LSF/SLURM 并行计算 |

Redhawk-SC |

支持GPU加速、分布式电源网络分析 |

NVIDIA GPU |

PowerArtist |

多线程并行波形处理 |

多核CPU |

史上最强大的--EDA/IC芯片/集成电路设计计算服务器存储集群配置方案

https://www.xasun.com/article/112/2799.html

如果你正在建设或升级EDA仿真平台,我可以根据你们企业设计规模(芯片类型/门数/节点数)进一步推荐采购级配置方案、预算评估表、网络与存储架构建议,也可提供国产替代工具链(如华大九天、芯华章)的对应配置建议。

咨询VX:wolf_chen1989

工程师必备

- 项目客服

- 培训客服

- 平台客服

TOP